Chip design has long been one of the most unforgiving engineering disciplines - a single logic error in a Register Transfer Level (RTL) file can cascade into expensive silicon respins. Now a team of researchers from Academia Sinica, National Taiwan University, National Cheng Kung University, and Harvard University is using AI to close that gap, introducing SiliconMind-V1, a multi-agent system built specifically to generate, verify, and fix Verilog hardware code.

How the 2-Part Framework Works

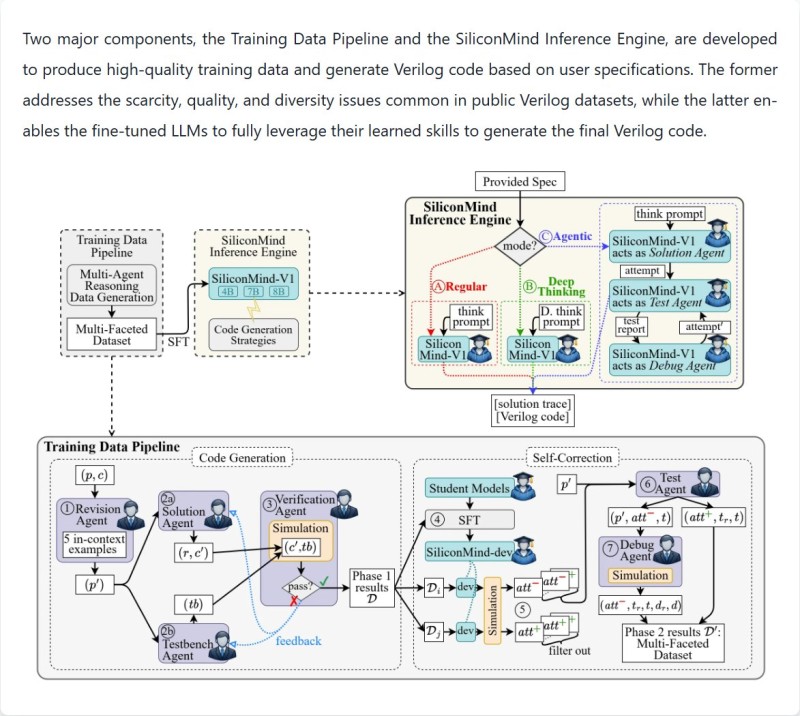

SiliconMind-V1 runs on two tightly linked components. The first is a training data pipeline that uses multi-agent workflows to simulate real hardware design and verification scenarios, producing reasoning-oriented datasets.

These datasets teach the model not just how to write syntactically correct Verilog, but how to reason about whether the code actually does what it is supposed to do. The second component is a dedicated inference engine that takes user specifications and iteratively generates, tests, and corrects RTL code using integrated testbench verification - automating a process that typically requires multiple human reviewers and software tools.

Outperforms QiMeng-CodeV-R1 on Functional Correctness

Inside that inference engine, specialized agents divide the labor: one handles revision, another proposes solutions, a third runs verification, and a fourth manages debugging. The structure mirrors how real hardware teams operate across tools and review cycles. Benchmark results show SiliconMind-V1 surpassing the current state-of-the-art QiMeng-CodeV-R1 model on functional correctness for RTL design tasks - while requiring less compute for training. That efficiency gap matters as semiconductor designs scale in complexity and teams look for ways to shorten development cycles without sacrificing reliability.

The project sits within a broader surge in agent-based AI. From AI systems generating $10,000 in autonomous work tasks to LlamaIndex and StackAI scaling agent workflows across millions of documents, the shift toward multi-step reasoning systems is accelerating across software, infrastructure, and now hardware. SiliconMind-V1 suggests that RTL design - long resistant to automation - may finally be ready for its AI moment

Saad Ullah

Saad Ullah

Saad Ullah

Saad Ullah